Objectives

The objective of this project was to designed, validated, and implemented a RISC-V-based microprocessor using the open-source SCR1 core on a Diligent Nexys A7 FPGA. Customized the SCR1 core for flexible configurations (RV32EC, RV32IC, RV32IMC) and developed an automated Tcl script to streamline the design workflow. Conducted functional verification, performance benchmarking with Dhrystone 2.1, and resource analysis to enhance energy efficiency and scalability for IoT and embedded systems, contributing to the RISC-V ecosystem through innovative automation and practical hardware implementation.

Socio-Economic Benefit

Cost Savings: Used open-source RISC-V and SCR1 core, cutting development costs for affordable IoT/embedded systems.

Energy Efficiency: Optimized low-power SCR1 designs, reducing operational costs and promoting sustainable tech.

Innovation Boost: Enabled scalable, customizable processors, fostering IoT/edge computing advancements and tech jobs.

Educational Value: Enhanced RISC-V ecosystem with automated workflows, supporting skill development in processor design.

Market Access: Facilitated cost-effective IoT solutions, improving technology access and digital inclusion in underserved regions.

Methodologies

Research & Planning: Conducted in-depth analysis of SCR1 documentation, RISC-V architecture, and toolchain capabilities to define system requirements and project scope.

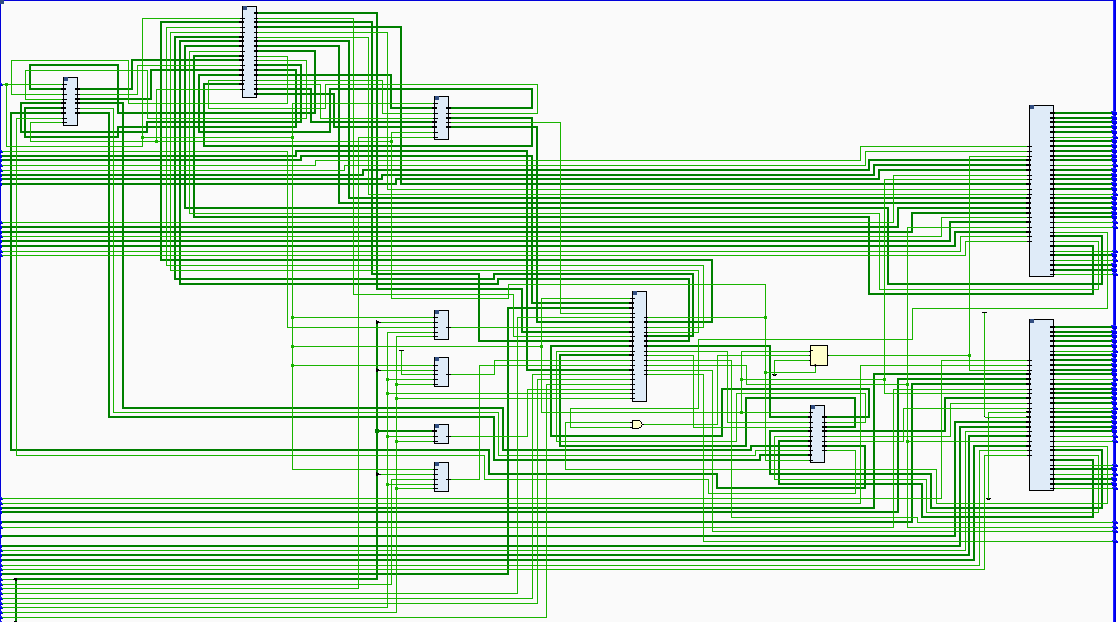

RTL Configuration: Cloned the SCR1 repository, set up version control branches for three configurations (RV32EC, RV32IC, RV32IMC), and customized parameters for each.

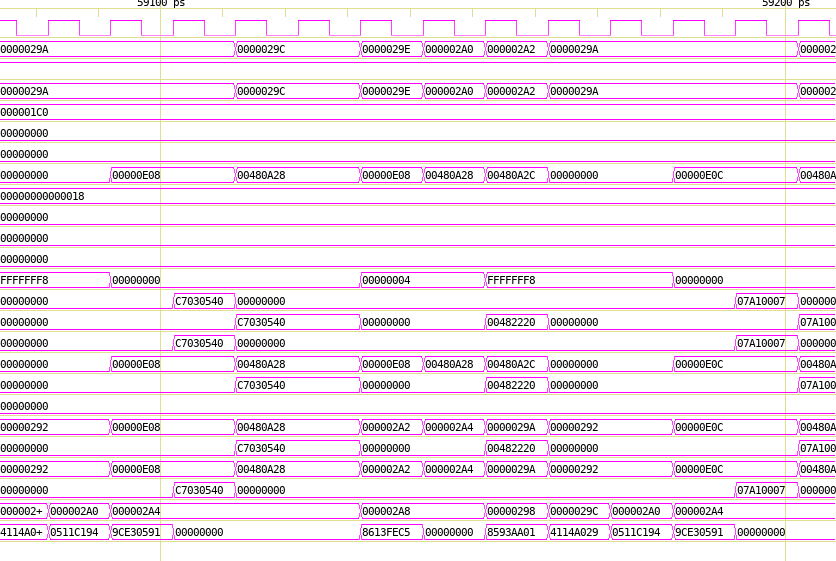

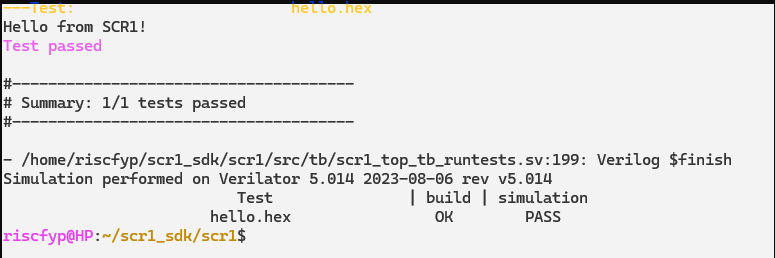

Simulation & Verification: Established a Verilator-based testbench, integrated RISC-V compliance tests, and developed custom test cases to ensure functional correctness.

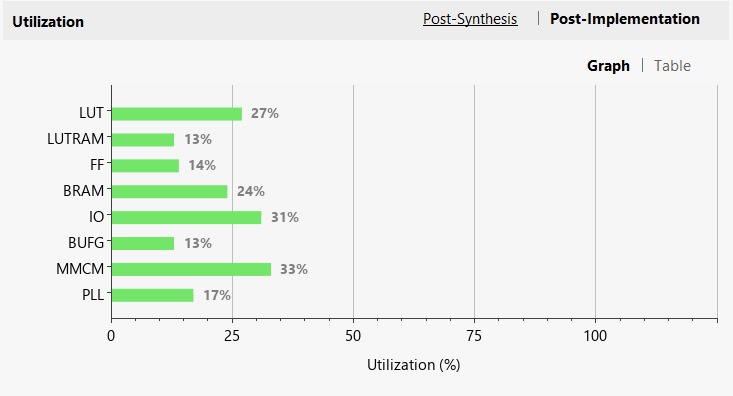

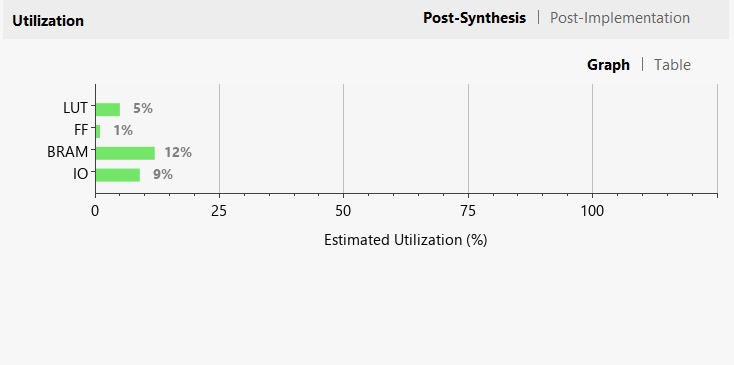

FPGA Synthesis & Implementation: Created Vivado projects for Nexys A7, applied board-specific constraints, and automated synthesis, implementation, and bitstream generation using Tcl scripts.

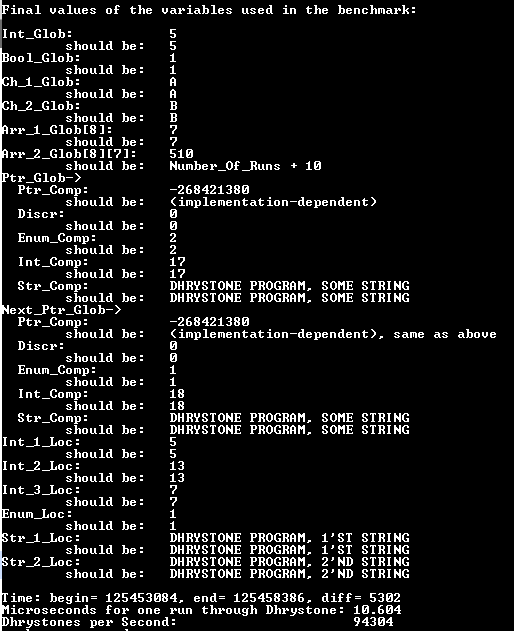

Performance Benchmarking: Cross-compiled Dhrystone 2.1 benchmark using RISC-V GCC, deployed to hardware, and measured performance metrics via UART and performance counters.

Analysis & Documentation: Compiled resource utilization, timing, and performance data into tables/graphs, and produced a detailed report to facilitate knowledge transfer and replication.

Outcome

The project successfully designed, validated, and implemented the SCR1 RISC-V core on the Digilent Nexys A7 FPGA, achieving three configurations (RV32EC, RV32IC, RV32IMC) with automated workflows. Key outcomes include:

Functional Validation: All configurations passed RISC-V compliance tests and a "Hello" test, confirming correct operation of debug, memory, and serial I/O subsystems.

Performance Metrics: Dhrystone 2.1 benchmarks yielded 4.48 DMIPS (Base, 223 µs/run) and 2.47 DMIPS (Max, 230 µs/run) at 1 MHz, demonstrating efficient MCU-class performance.

Resource Efficiency: Post-implementation FPGA utilization was modest (27% LUT, 14% FF, 24% BRAM, 31% I/O), suitable for resource-constrained designs.

Automation: Developed Tcl scripts for end-to-end Vivado automation, streamlining project setup, synthesis, and bitstream generation.

Documentation: Produced a comprehensive report with design details, results, and best practices, aiding future RISC-V research and replication.